Course of lectures “Computers, systems and networks. Computers, complexes, systems and networks Computers, complexes, systems and networks laboratory

Send your good work in the knowledge base is simple. Use the form below

Students, graduate students, young scientists who use the knowledge base in their studies and work will be very grateful to you.

MINISTRY OF EDUCATION AND SCIENCE OF RUSSIA

Branch of the federal state budgetary educational institution

higher professional education

"Samara State Technical University" in Syzran

Department of Informatics and Control Systems

Settlement and explanatory note

for course work

"Computers, systems and networks"

Performer: student gr. EABZ-301

Golovin K.O.

Head of the Kyrgyz Republic: Ph.D., Associate Professor

Tarakanov A.V.

Content

- 1. Introduction

- 2. Description of the microprocessor

- 3. Description of operations

- 4 Program code for the illustrated processor

- 5 . Block diagram of the program

- 7. Conclusion

- 8. Bibliography

1. Introduction

Currently, many models of microprocessors are produced with a very wide range of parameters. This course project describes a hypothetical microprocessor with an architecture (i.e., structure and language) that has typical features of modern microprocessors. Although our hypothetical microprocessor is not commercially available, it is close to some real-life models, such as Intel's 8000 series processors.

A microcomputer is a system with a bus organization, consisting of modules, or blocks, implemented in the form of large and ultra-large integrated circuits. These modules process information, control the flow and interpretation of commands, manage buses, store information, and communicate between the computer and its environment.

The first four functions are usually performed by one functional unit - the microprocessor. The functions of storing information are performed by a storage device. It may include both constant and RAM. Finally, external communications are carried out by blocks called I/O ports. Each such port is an interface between the microprocessor and: some external device, such as a terminal (display and keyboard), external memory for storing large amounts of information, a process controller or a measuring device.

The main task of the microprocessor is to execute program code (commands). Both instructions and the data they process are stored in memory in the same form - namely, as binary numbers. The use of the binary number system can significantly simplify the design of the microprocessor and other computer systems. Programming for technological microprocessors, for which there are no translators from high-level languages, is carried out by directly specifying operands and instruction numbers using, however, not binary, but a more convenient hexadecimal number system.

The structure of a microcomputer consisting of similar blocks is shown in Figure 1.

Figure 1 - Structure of a microcomputer with a bus organization

The interaction of blocks is carried out using three types of buses: address buses, data buses and control buses.

For the course work, a hypothetical (illustrated) microprocessor with a set of instructions and an array of five elements - positive integers - is given. With the elements of this array, it is necessary to perform the following list of operations to be programmed:

1. Operation No. 6. - transition to a subroutine with parameters passed through the stack.

2. Operation No. 4 - cycle (addition of all array elements).

3. Operation No. 7 - multiplication of two array elements.

4. Operation No. 5 - transition to the subroutine with passing parameters through registers.

5. Operation No. 3 - finding the largest element of the array.

6. Operation No. 2 - addition of array elements with a constant.

7. Operation No. 1 - addition of any two array elements.

2. Description of the microprocessor

Figure 2 depicts the general structure of a hypothetical illustrative microprocessor.

Figure 2 - Structure of a hypothetical microprocessor

The components included in it indicate that it is a software-controlled processor. Several components, namely the program counter (program counter), stack, and instruction register, are used to process instructions.

Components such as ALU, carry flip-flop, general registers (or work registers), and data address register serve to process the data. All other components, namely the command decoder and the control and synchronization unit (BUS), control the operation of other components. The interaction of components is carried out via internal data transmission channels. The microprocessor communicates with other blocks (storage and input/output devices) via the address bus, data bus and control bus.

The microprocessor works with words consisting of 8 bits. These words, called bytes, are useful for performing arithmetic and logical operations. If numbers of “greater length” are encountered in calculations, then special programs for calculations with "double precision", "triple precision", etc.

On the other hand, an 8-bit address allows you to directly address only 2 8 = 256 memory cells. For real problems this, of course, is not enough. Therefore, 16 bits (two bytes) are usually used to specify a memory address, and this allows 2 16 = 65,536 cells to be directly addressed.

Information is transferred to and from the microprocessor via buses. Data buses consist of 8 lines according to word length, while the address bus consists of 16 lines. As shown in Figure 2, the address bus is unidirectional and the data bus is bidirectional. The control bus consists of 5 lines leading to the control and synchronization unit and 8 lines leaving it. These lines transmit control and timing signals between the components of the microprocessor and between the microprocessor and other blocks of the microcomputer.

The program counter consists of 16 bits and contains the address of the next command byte read from memory. It is automatically incremented by one after each byte is read. There is a connection between the program counter and the top of the 64 register stack. One of the functions of the stack is storing the return address from a subroutine. The stack can also store data from the upper three general registers and the carry flip-flop.

While a data word is always one byte, a command can be one, two, or three bytes. The first byte of any instruction comes from memory via the data bus to the instruction register. This first byte is fed to the input of the command decoder, which determines its meaning. Specifically, the decoder determines whether the command is a single-byte command or whether it consists of more bytes. In the latter case, additional bytes are transferred along the data buses from memory and received either in the data address register or in one of the general registers.

The data address register contains the operand address for instructions that access memory, the port address for I/O instructions, or the next instruction address for jump instructions.

Fifteen 8-bit general registers contain operands for all data-operating instructions. To specify these registers, 4-bit codes from 0000 to 1110 are used. Register 0000 is called the accumulator (ACC) and is involved in all arithmetic and logical operations. Specifically, it contains one of the operands before the operation is performed and receives the result after it completes. Typically, access to general registers is made using the K-selector or r-selector. The R selector allows access to any register, while the r selector only allows registers 0000, 0001, and 0010 to be accessed.

Very useful opportunity present in many machines is indirect addressing. Setting the non-existent general register 1111 is used as an indication to access a byte of memory at a 16-bit address, which is obtained by combining the contents of two fixed general registers. Namely, the upper 8 bits of the address are from register 0001 (H), and the lower 8 bits of the address are from register 0010 (L). To explain this indirect addressing, let's assume that register 0001, i.e. register H contains 1011101, and register 0010, i.e. register L contains 00101011. Then any instruction referencing register 1111 will cause the operand to be fetched from memory location 101110100101011.

programming microprocessor program code

All arithmetic and logical operations are executed in an arithmetic logic unit (ALU). The ALU inputs are two 8-bit buses. One of them comes from the accumulator (register 0000), and the other from R. - a selector that selects either one of the general purpose registers from 0000 to 1110, or a memory cell if indirect addressing is specified. Another input line comes to the ALU from the carry flip-flop C, which is involved in some arithmetic and logical operations.

The results from the ALU are transferred to the accumulator via the 8-bit output bus. There are two more lines going from the ALU to the control and synchronization unit; they convey information about the presence or absence of two special conditions: the accumulator contains zeros (line Z) and the most significant digit of the accumulator is 1 (line N). The second line is very convenient when working with numbers in two's complement code, when the most significant bit is signed, and 1 corresponds to negative numbers. The carry flip-flop and both ALU status lines Z and N are called flags and are used in conditional jump instructions.

The last component of the microprocessor is the control and synchronization unit (BUS). It receives signals from a command decoder, which parses the command. As already mentioned, the BUS receives signals from the ALU and the transfer trigger that determine the conditions for control transfers. All other components of the microprocessor receive from the BUS the control and synchronizing signals necessary to execute the command. Using 13 external lines, the control device interfaces with other microcomputer modules.

3. Description of operations

1. Program download operation.

A special loader program performs operations to input the required program from some input device and place it in memory. The main procedure calls the input subroutine four times to enter the first four address words, transferring these words each time to new general registers. Then the cycle of transferring the entered words into memory begins. Each word is entered by the input routine and then transferred to the corresponding memory location, the address of which is given by the current address value (TA). TA increases by 1 each time the cycle passes, i.e. as each word arrives. At the end of the cycle, a check is made to see if TA does not exceed the value of the final address (KA). If so, the boot procedure ends; otherwise, the cycle repeats. The bootloader program begins in cell 0000. The program accesses two input ports: port 00 for status information and port 01 for data. The first group of commands corresponds to the main procedure. The input routine starts at location 001D. General registers 1, 2, 3 and 4 store TAN TAL, KA H and KA L respectively. They are loaded with address information coming from the input device. To do this, each time the command to switch to the subroutine and the transfer command are executed.

The cycle begins with a command to jump to the input subroutine. After returning from it, the next entered word is in the accumulator. This word is transferred to the memory location using the indirect addressing mechanism present in the exemplary microprocessor. Namely, the MOV O to F instruction transfers the contents of the accumulator to a memory cell whose address is given by the contents of registers 1 and 2 (i.e. H and L). Since these registers contain the value TA, the word ends up in the correct memory location. The next team, IHL, increases the TA value by 1. Comparison of the addresses of TA and KA is carried out using a double-precision subtraction procedure and subsequent conditional jump. For double-precision subtraction, the lower parts TA and KA are first subtracted, and then the higher parts, involving the loan remaining from the lower parts. The final loan remains in trigger C. The next command is “jump at zero carry” to the beginning of the loop. When C = 0 we enter the loop again, when C = 1 the program stops.

2. Operations No. 6 - the operation of jumping to a subroutine with passing parameters through the stack.

The first two instructions fill the H and L registers with the high and low parts of the address of the first number, respectively. The next PUSH instruction pushes the values of these registers onto the stack. After which the stack is lowered twice. The second number is pushed onto the stack in the same way. After the data has been pushed onto the stack, it jumps to a routine that unloads the stack using the POP instruction. Data retrieved from the stack is transferred to memory cells using the STR command. RET command - exit from the subroutine.

3. Operation No. 4 - addition of all array elements.

The first two commands enter the address of the first number in H and L. Then an initial value of 5 is placed in register 3. Register 3 will act as a counter for the number of numbers being added. The amount is accumulated in general register 4, and the initial zero value is entered into it. Finally, the constant 1 is loaded into general register 5, which will be subtracted from the counter during the process of summing the numbers. The working part of the loop begins by loading the current private sum into the accumulator from register 4. This is followed by the addition instruction ADD F, containing a special pointer F, which actually corresponds to a main memory cell with an address in a pair of registers H and L. The contents of this cell are added to the private amount in the battery. After this, the result is transferred to general register 4. Next, the IHL instruction modifies the H and L registers so that they contain the address of the data that should be processed in the next iteration. The contents of the loop counter are then transferred to the accumulator, decremented by 1, and returned to register 3. When the computation is completed, the accumulator will be 0. This condition is tested by the "conditional jump when accumulator is non-zero" command. If the accumulator is 0 then no transition occurs and the program exits to the stop command, otherwise the next iteration is executed.

4. Operation No. 7 - the operation of multiplying two array elements.

The registers are distributed as follows: R 2 is the iteration counter, R 3 is the multiplicand 1 element of the array, R 4 is the multiplier 2 element, R 5 is the high part of the product rn, R 6 is the low part of the product P L . The operation begins with the initialization of the cycle - setting zeros in the registers of the high and low parts of the products, setting the initial value of the counter. Then the 1st factor is loaded into the accumulator from register 4, the multiplier is shifted cyclically to the right and the result is returned to register 4. Thus, the next digit of the multiplier, which determines the partial product, ends up on the carry trigger C. Then, to prepare the addition and shifts, the highest part of the product pH is transferred to the battery. Testing C = 1 is carried out by the “transition with non-zero carry” command. It ensures that the next command is skipped when C=0. This next instruction adds a 2nd multiplicand to the accumulator (which contains pH) and stores the carry from the most significant position to C. Ph and C are then cyclically shifted to the right by the RTR instruction. After the shift, the new value рн returns to register 5. Then p l and C are shifted to the right, for which p l from register 6 is loaded into the accumulator, cyclically shifted along with C and the result is returned to register 6. After this, the counter in register 2 is decreased by 1 by the command DHL, the result is transferred to the accumulator and tested with the “transition when accumulator is non-zero” command. If the accumulator contains 0, then the subroutine is exited; otherwise, control is transferred to the beginning of the loop.

5. Operation No. 5 - the operation of switching to a subroutine with passing parameters through registers.

The LDR 0 instruction loads the first number into the accumulator, then the MOV instruction transfers the data to register 5. Next, the second number is loaded into the accumulator and the data is transferred to register 6. The third number is loaded in the same way, the data is transferred to register 7. Then there is a transition to the subroutine, which transfers data from registers 5, 6, 7 to memory cells using the MOV and STR instructions. RET command - exit from the subroutine.

6. Operation No. 3 - finding the largest element of the array.

The LDR 0 instruction loads 1 element into the accumulator, the LDR 1 instruction places the 2nd element into the common register 1. They are then compared by subtracting 2 from 1. If the 2nd element is strictly greater than the first, then there is a loan to the most significant bit, which is stored as a one in transfer trigger C. However, even before checking the transfer C, the value of the 1st, as a “test”, the largest of the 1st and 2nd, is loaded into register 2. Then the conditional jump command is executed on the value of C. If C is not equal to zero, then the candidate to the role of the largest, i.e. 1 element, is replaced by 2 element. If C = 0, then the transition to loading the third element of the array occurs, and in this case the third remains as the larger value - subtraction of 1 and 2 from the largest numbers occurs, and the presence of a loan is checked. If there is a loan, then the 3rd is greater and the 3rd is transferred to register 2, replacing the largest of 1 and 2. In any case, the largest value of the numbers is in register 2, and it will be similarly compared with the next 4 element, and then the fifth element of the array. After comparing all 5 numbers, the STR 2 instruction transfers the contents of register 2, i.e. the largest value of the numbers into the memory cell.

7. Operation No. 2 - addition of array elements with a constant.

The LDR 1 command loads the 2D constant into register 1, the LDR 0 command loads 1 element of the specified array into the accumulator. Then, using the ADD 1 instruction, the value stored in the accumulator is added with the value stored in register 1. The result of the sum is transferred to the memory cell using the STR instruction. Then the remaining elements of the array 2,3,4,5 are similarly loaded into the accumulator and added to the constant. A one-byte constant is loaded into the R3 register, and in the R5 register there is a counter for a cycle of searching through all the elements of the array.

8. Operation No. 1 - addition of any two array elements.

The LDR 0 command loads the 1st number into the accumulator, the LDR 1 command loads the second number into register 1. The loaded numbers are then added using the ADD 1 command. The result of the sum is stored in the accumulator. The STR 0 instruction transfers the accumulator value to the memory location.

4. Program code for the illustrated processor

|

Machine language command |

Command in symbolic form |

A comment |

||

|

Loader program |

||||

|

Calling the input subroutine for TA N |

||||

|

Applying for TA L |

||||

|

Application for CA N |

||||

|

Appeal for KA L |

||||

|

The word entry cycle begins |

||||

|

Transferring a word to M [TA] |

||||

|

TA + 1 - >TA. |

||||

|

Double precision subtraction of TA from KA |

||||

|

C=1 is set if TA > KA |

||||

|

Checking a loan in C. If there is no loan |

||||

|

entering a new word |

||||

|

Go to Operations |

||||

|

Start of the input program. Entering a word |

||||

|

condition. |

||||

|

Checking the character bit in the status word. |

||||

|

If 0, repeat check |

||||

|

Entering a word into the battery from the device |

||||

|

Return from subroutine |

||||

|

Operation№6 |

||||

|

first element |

||||

|

Pushing onto the stack |

||||

|

Setting the addresses in registers H and L |

||||

|

second element |

||||

|

Pushing onto the stack |

||||

|

Go to subroutine in cell 00F4 |

||||

|

Operation№4 |

||||

|

Setting the addresses in registers H and L |

||||

|

first element |

||||

|

Setting the initial value |

||||

|

loop counter equal to 5 |

||||

|

Setting the private sum to 0 |

||||

|

Adding a number |

||||

|

Increase H and L |

||||

|

Decrement counter by 1 |

||||

|

End of loop check |

||||

|

Transferring the contents of ACC to cell 0107 |

||||

|

Operation№7 |

||||

|

Setting zero values in Rн and R L |

||||

|

Installation on the initial counter |

||||

|

values 8 |

||||

|

Cyclic shift to the right, ml. the Ass bit hits C |

||||

|

Remembering the shifted multiplier |

||||

|

Multiplier bit test. Transition at 0 |

||||

|

Adding a multiplicand with st. part of the work |

||||

|

Shift pH to the right, ml. bit in C |

||||

|

Remembering the shifted Rн |

||||

|

Shift C and ml. parts of the work to the right |

||||

|

Remembering the shifted R L |

||||

|

Decrement counter by 1 |

||||

|

Testing Ass. Repetition |

||||

|

loop if not null |

||||

|

Transfer Art. parts of the work in register 1 |

||||

|

Transfer ml. parts of the work in register 2 |

||||

|

Transferring the contents of register 1 to location 0108 |

||||

|

Transferring the contents of register 2 to location 0109 |

||||

|

Operation№5 |

||||

|

Go to subroutine in cell 00E7 |

||||

|

Operation№3 |

||||

|

Transferring the 1st element from memory to ACC |

||||

|

Transfer 2nd from memory to register 1 |

||||

|

Subtraction 2 el. from 1el. Trigger C is installed if 2 el. more than 1 |

||||

|

Transferring 1 number to register 2, as large as possible |

||||

|

Checking C for the presence of a loan. If there is no loan then 1 > 2 and the next command is omitted |

||||

|

Pass 2 array elements to register 2, replacing 1 if 2 > 1 |

||||

|

Transferring 3 array elements from memory to register 1 |

||||

|

Transferring the largest of the 1st and 2nd to the battery from reg.2 |

||||

|

Subtracting 3 from the largest among 1,2 numbers. C is set if 3 is greater |

||||

|

Checking C for the presence of a loan. If there is a loan, then 3 is greater, otherwise, the next command is omitted. |

||||

|

Passing 3 to register 2, replacing the largest of 1 and 2 numbers if 3 is greater |

||||

|

Transferring 4 array elements from memory to register 1 |

||||

|

Passing the largest of 1,2,3 numbers to the accumulator from register 2 |

||||

|

Subtracting the 4th from the largest among 1,2,3. C is set if 4th is greater. |

||||

|

Checking C for the presence of a loan. If there is a loan, then 4 |

||||

|

more, otherwise the next command is omitted. |

||||

|

Passing 4th to register 2, replacing the largest of the array 1,2,3 if 4 is greater |

||||

|

Transferring array element 5 from memory to register 1 |

||||

|

Passing the largest of array elements 1,2,3,4 to the accumulator from register 2 |

||||

|

Subtracting 5 from the largest among 1,2,3,4. C is set if 5 is greater |

||||

|

Checking C for the presence of a loan, if there is a loan, then 5 is more, |

||||

|

otherwise, the next command is omitted. |

||||

|

Passing 5 to register 2, replacing the largest of 1,2,3,4 if 5 is greater. |

||||

|

Transfer of the largest element to cell 010A |

||||

|

Operation№2 |

||||

|

Addition of 1 number with a constant, sum As |

||||

|

Transferring the contents of ACC to cell 010B |

||||

|

Transferring the contents of a memory cell |

||||

|

Addition of 2 numbers with a constant, sum As |

||||

|

Transferring the contents of ACC to cell 010C |

||||

|

Transferring the contents of a memory cell |

||||

|

Addition of 3 numbers with a constant, sum As |

||||

|

Transferring the contents of ACC to cell 010D |

||||

|

Transferring the contents of a memory cell |

||||

|

Addition of 4 numbers with a constant, sum As |

||||

|

Transferring the contents of ACC to cell 010E |

||||

|

Transferring the contents of a memory cell |

||||

|

Addition of 5 numbers with a constant, sum As |

||||

|

Transferring the contents of ACC to cell 010F |

||||

|

Operation№1 |

||||

|

Transferring the contents of a memory cell |

||||

|

Transferring the contents of a memory cell |

||||

|

0103 to register 1 |

||||

|

Addition of 0 and 1 registers, sum Ac |

||||

|

Transferring the contents of ACC to cell 0110 |

||||

|

Endingoperations |

||||

|

Stopping the program |

||||

|

Start of the subroutine for operation No. 5. Transferring the contents of register 5 to ACC |

||||

|

Transferring the contents of ACC to cell 0111 |

||||

|

Transferring the contents of register 6 to register 1 |

||||

|

Transferring the contents of register 1 to location 0112 |

||||

|

Transferring the contents of register 7 to register 2 |

||||

|

Transferring the contents of register 2 to location 0113 |

||||

|

Return from operation subroutine No. 5 |

||||

|

Start of the subroutine for operation No. 6. Popping data from the stack |

||||

|

Transferring the contents of register 1 to location 0114 |

||||

|

Transferring the contents of register 2 to location 0115 |

||||

|

Popping data from the stack |

||||

|

Transferring the contents of register 1 to location 0116 |

||||

|

Transferring the contents of register 2 to location 0117 |

||||

|

Return from operation subroutine No. 6 |

||||

|

1 array element |

||||

|

2 array element |

||||

|

3 array element |

||||

|

4 element of the array |

||||

|

5 array element |

||||

|

The result of adding all the numbers |

||||

|

The result of multiplying two numbers (art. part) |

||||

|

The result of multiplying two numbers (lower part) |

||||

|

The result of finding the largest number |

||||

|

The result of adding 1 number with a constant |

||||

|

The result of adding 2 numbers with a constant |

||||

|

The result of adding 3 numbers with a constant |

||||

|

The result of adding 4 numbers with a constant |

||||

|

The result of adding the 5th number with a constant |

||||

|

Result of adding 2 numbers |

||||

|

Register data |

||||

|

Register data |

||||

|

Register data |

||||

|

Stack Data |

||||

|

Stack Data |

||||

|

Stack Data |

||||

|

Stack Data |

5. Block diagram of the program

Posted on http://www.allbest.ru/

Posted on http://www.allbest.ru/

Posted on http://www.allbest.ru/

6. Maps of information flows

The execution of any command consists of two stages. The first stage is reading the command from memory. Reading each byte takes one machine cycle (three clock cycles). After reading the first byte (operation code) that goes into the command register, the control unit determines how many bytes the command consists of. If there are one or two more bytes, then it takes one or two machine cycles to read them. These bytes go into the data address register. The second stage is the execution of the command. Some instructions are executed in the last cycle of the machine cycle, while others require another machine cycle to complete (register load and store instructions and instructions that use indirect addressing).

Let's present maps of information flows for operation No. 6. The program for operation No. 6 consists of the following operations: LRI, PUSH, JMS, POP, STR, RET.

Figure 3 - Information flow map for the LRI team

The LRI command is a two-byte command; its peculiarity is that the data is part of the command itself; using such a command it is very convenient to set constants. The byte fetched in the first cycle is placed in the command register, and the byte fetched in the second is placed in the data address register. After this, unless R is equal to 1111 2 , the instruction is completed on the third clock pulse on the second machine cycle. The lower 8 bits of the data address register, containing the second byte of the command, are transferred to the general register R. After sampling and decryption, the second byte from the data bus is supplied to the data address register, after which it is transferred from there to the R selector, where the register specified in the command is fetched.

One of the special commands in the program code is the one-byte PUSH command, which is used to push data onto the stack. The stack goes down twice. As a result, the second register of the stack contains the value of the accumulator with the carry, and the first (top of the stack) contains the contents of a pair of registers H and L. The map of information flows is shown in Figure 4.

Figure 4 - Information flow map for the PUSH command

Next in the given operation number 6 is a JMS command, which contains three bytes and serves as a command to call the subroutine. The stack is lowered and the contents of the program counter are pushed onto the top of the stack. The contents of the last stack register are lost. The contents of the program counter are replaced by the second and third bytes of the JMS command, with the second byte replacing the high 8 bits of the program counter and the third byte replacing the low 8 bits, causing control to be transferred to the specified cell. The map of information flows is presented in Figure 5.

Figure 5 - Information flow map for the JMS command

The next special code instruction is the one-byte POP instruction, which is used to pop data from the stack. The contents of the top of the stack are transferred to a pair of registers H and L. The contents of the low half of the second stack register are transferred to the accumulator, and the low bit of the high half of the same register is transferred to the carry flip-flop C. The stack is raised twice, the state of the two lower registers remains unchanged. The map of information flows is presented in Figure 6.

Figure 6 - Map of information flows for the POP command

The STR R command is three bytes. It serves to remember the register, and the second and third bytes of this command contain the high and low parts of the memory cell into which it is necessary to save the contents of the register we need. The contents of the data address register, loaded in the fetch-decryption phase by the second and third bytes of the instruction, are supplied to the address bus, and the contents of the general register r are supplied to the data bus. The control device then generates a “write” signal that strobes the writing of data to the addressable memory cell. The execution phase requires one external exchange and takes one machine cycle. Therefore, a complete instruction cycle takes four machine cycles: three for the fetch-decryption phase and one for the execution phase. The map is shown in Figure 7.

The final command for accessing subroutines is the return command from the subroutine RET, which contains one byte. The stack is lowered and the contents of the program counter are pushed onto the top of the stack. The contents of the last stack register are lost.

The contents of the program counter are replaced by the second and third bytes of the JMS command, with the second byte replacing the high 8 bits of the program counter and the third byte replacing the low 8 bits, causing control to be transferred to the specified cell. The map of information flows is presented in Figure 8.

Figure 7 - Information flow map for the STR command

Figure 8 - Information flow map for the RET command

7. Conclusion

During the course work, the principles of operation of a hypothetical microprocessor were studied. The instruction system of an illustrative microprocessor, its sampling, decoding and control phases, addressing methods, machine-level programming principles, and block diagram design were examined in detail.

Modern microprocessors used in personal computers, their architecture is very similar to this hypothetical processor. The differences are mainly that modern processors have more developed hardware functions (such as hardware multiplication, division, cyclic operations), a more convenient indirect memory addressing system, etc.

8. Bibliography

1. Wirth N. Algorithms and data structures. - M.: Mir, 1999.

2. Givone D., Rosser R. Microprocessors and microcomputers. - M.: Mir, 1993.

3. Goodman S., Hidetniemi S. Introduction to the development and analysis of algorithms. - M.: Mir, 1991.

4. Kagan B.M. Electronic computers and systems. - M.: Enegroatomizdat, 1997.

5. Guidelines for completing a course project for students in the discipline "Computing, machine systems and networks." 2003

6. Pyatibratov A.P., Gudyno L.P., Kirichenko A.A. Computing systems, networks and telecommunications. - M.: Finance and Statistics, 2002.

Posted on Allbest.ru

Similar documents

The procedure and rationale for choosing a microprocessor, its connection diagram. Organization of input-output and memory of the microprocessor. Development and testing software based on the eight-bit MP Z80. Methods for increasing the operating frequency of a microprocessor.

course work, added 01/03/2010

Characteristics of the Z80 microprocessor, its advantages and command system. Design of the interface, block diagram and operating algorithm of the control microcomputer. Development of memory modules, clock generator, controller, input/output and indicator.

course work, added 02/17/2014

Analysis of the processing part of the microprocessor. The main elements of a microprocessor, their interaction during its operation. Methods for solving examples in binary system calculus. Purpose of microprocessor blocks. The principle of operation of the laboratory installation.

laboratory work, added 09/26/2011

General characteristics of operations performed by commands of the base system. Description and mnemonic codes of commands used when developing a program in AVR Assembly language. Basic principles of operation of commands accessing SRAM addresses and I/O registers.

abstract, added 08/21/2010

Arithmetic-logical device of the microprocessor: its structure and components, purpose, functions, main specifications. Organization of microcomputer input/output system. The actual operating mode of the microprocessor, its meaning and description.

test, added 02/12/2014

Video adapters (display processors) are specialized processors with their own set of instructions, specific data formats and their own program counter. Graphics video adapters - random scan and raster type adapters.

lecture, added 08/15/2008

Development and description of a general algorithm for the functioning of a digital notch filter based on a microprocessor system. Justification of the hardware of the device. Debugging a program in the microprocessor command language. Calculation of speed and stability.

course work, added 12/03/2010

Determination of the main parameters of the microprocessor. Development of a structural, functional and circuit diagram, calculation of time parameters. Principles of forming the structure of software and determining the basic requirements for it.

course work, added 06/14/2014

Development of a block diagram of the device. Study of principle electrical diagram devices with a description of the purpose of each element. Characteristics of the software: sections of declarations, microprocessor initialization and main loop.

course work, added 11/14/2017

Development and description of the device operation algorithm, debugging work program in the microprocessor command language. Justification of the hardware of the device. Drawing up an electrical circuit diagram of the device, calculating the speed of the device.

Part 1. Computers. 3

Lecture 1. Structure of a computer. 3

Lecture 2. The evolution of microcomputers. 21

Lecture 3. Machine organization of the 80286 processor 29

Lecture 4. Operands and operand addressing modes. 42

Lecture 5. General organization of memory. 51

Lecture 6. Interrupting the microprocessor in a computer. 54

Lecture 7. Serial interface RS-232C. 61

Lecture 8. Serial interface COM port. 69

Lecture 9. Programmable communication interface. 77

Lecture 10. Data transfer between computers using modems.

Types and characteristics of modems. A set of AT commands. 85

Lecture 11. Programmable peripheral interface. 95

Lecture 12. Parallel interface: LPT port. Ponyukhov E. V. 102

Lecture 14. Universal Serial Bus USB. 121

Lecture 15. USB bus protocol. 133

Lecture 16. IEEE-1394 (FireWire) interface. 148

Lecture 17. Organization of direct memory access. 151

Lecture 18. Computer input devices. Keyboard. 158

Lecture 19. Computer interface with video terminal. Video adapter.

Image modes: text and graphic modes. Video memory.

Animation of images. 168

Lecture 20. Magnetic disk drive: flexible and hard.

Disk structure: tracks, sectors, blocks. Exchange of information between computers and magnetic disks. 176

Lecture 21. Scanner.

Reading the image. Types of processed images. Image quality. 181

Lecture 22. Purpose and functions of the operating system. 190

Part 2. Computing systems. 202

Lecture 23. Classification of parallel data processing systems. 202

Lecture 24. Classification of multiprocessor systems according to the method of organizing main memory. 211

Lecture 25. Review of architectures of multiprocessor computing systems. 217

Lecture 27. Principles of constructing telecommunications computing systems. 247

Part 3. Computer networks. 253

Lecture 28. Reference model of open systems interaction. 253 Lecture 29. Local computer networks. 262 Lecture 30. Wireless networks based on GPRS service. 277

Lecture 31. Radio-Ethernet wireless networks. 285

Lecture 32. Wireless local networks on

Wi-Fi based

- technologies. 292

Part 1. Computers.

Lecture 1. Structure of a computer.

1.1 General structure

Personal computer (PC, PC – Personal Computer) is a device for programmable data processing. A PC allows complex sequences of computational operations to be carried out without human intervention.

Typically, personal computers consist of devices:

System unit (to house the main elements of the computer)

It is known that you can improve your PC by adding new or replacing old components. Therefore, when choosing a case, it is recommended to be guided not only by aesthetic criteria, but also take into account its functionality.

Although the case looks the least impressive of the computer parts, it contains all the main components of the computer

Electronic circuits that control the operation of a computer (microprocessor, RAM, device controllers, etc.)

A power supply that converts mains power into low-voltage direct current that is supplied to the computer's electronic circuits

Floppy disk drives (or drives) used for reading and writing floppy disks (floppy disks)

Hard drive magnetic disk, designed for reading and writing to a non-removable hard disk (hard drive)

Through special sockets (connectors), usually located on the back wall of the case, you can connect various devices to the computer.

These devices are connected using special wires (cables). To protect against errors, the connectors for inserting these cables are made different, so that the cable simply will not be plugged into the wrong socket.

The body consists of two U-shaped tin or steel sheets inserted into each other. On one of the sheets is attached motherboard and the other leaf is the cover.

Typically, the front panel of the case contains several buttons (power button and Reset button to restart the PC) and LED indicators (LED - Light Emiting Diode) to indicate power on and operation of the hard drive. Sometimes there are digital indicators of the processor frequency.

Inside, on the front panel of the case, there is a speaker (PC Speaker), which is a standard means of delivering acoustic signals.

Along with the case you purchase a power supply. The size of the power supply is determined by the design of the case. There are many modifications of power supplies different types. They all differ in power output.

Case types:

Slimline-(thin) – in its structure it belongs to compact cases. They are indispensable where every centimeter of the desktop is valuable. In such a case, virtually all the internal space is used. And although the design of the case saves space, if it is necessary to replace a component element, you have to disassemble almost the entire system unit.

Desktop-(desk) - until recently the most commonly used case. The biggest drawback is that they take up a lot of space on your desktop. As a rule, the width of such cases is about 45 cm and the height is about 20 cm.

Tower-(tower) – significantly saves space on your desktop. Roughly speaking, this is a Desktop placed on its side. There are several modifications of such cases that differ from each other in height: Mini-Tower (about 40 cm in height), Midi-Tower (about 50 cm), Big-Tower (about 60 cm).

ATX type case - In July 1995, Intel proposed a new specification for the design of the PC case (and motherboard). Currently, this specification is accepted by all leading PC manufacturers. The emergence of the ATX specification is due, on the one hand, to increased requirements for processor speed and, accordingly, thermal conditions inside the case, as well as an increase in the number of chips on the motherboard (the emergence of all-in-one systems, that is, when video and audio are integrated on the motherboard cards, drive controllers, etc.). On the other hand, there were demands for more convenient and simpler access to the internal elements of the PC. If you opened the lid of a PC case and installed new components (expansion cards, hard drive, etc.), you probably encountered a lot of inconveniences: cables of peripheral devices block access to memory modules, the CPU blocks the ability to install full-size cards in expansion slots, etc.

According to the ATX standard, the motherboard is rotated 90°, as a result of which all expansion slots become suitable for using full-size motherboards, and the CPU is located under the power supply, and the power supply fan additionally blows the processor.

Externally, the ATX case is similar to the Desktop and Tower type cases, however:

The ATX case is equipped with a new power supply, which differs from its predecessors in size, design and the presence of a new connector for connecting to the motherboard

All expansion slots support full-size boards

Integrated ports reduce the number of cables and wires inside the case, making it easier to access motherboard components

All I/O ports are located on one side of the motherboard in one row and go to the rear wall of the case (video, audio and game port can also be located here)

The interface connectors for disk drives and hard drives are located next to the seats for 3.5" drives, therefore, shorter cables can be used

Currently there is a large number of ATX cases such as Desktop, Mini-Tower, Tower.

The modern information system of even a small enterprise consists of the most various devices (desktop computers, servers, mobile devices, network equipment, input control devices, etc.), which must work consistently, stably and safely. Information systems of large enterprises require multi-platform integration of cloud servers, remote data processing centers, encryption and access control servers, terminal stations and servers, wired and wireless networks, Internet telephony, user support systems, a wide variety of application software. A modern system administrator must have fundamental knowledge and the ability for constant self-education. Training in this profile allows you to form the basis for a successful professional career in the design, creation, operation and development of computer complexes, systems and networks of enterprises and organizations.

The purpose of training is to develop the following abilities:

- Design (using computer-aided design systems), modeling, design and development of computer networks and complexes of organizations and enterprises;

- Conducting audits and diagnostics of information technology resources of enterprises and organizations;

- Implementation and development of systems information security and reliability of data storage;

- Administration of local and distributed computer networks;

- Configuring, testing and maintaining network equipment;

- Manage multi-platform integration of networks and devices running on different operating systems;

- Operation of complexes, systems, networks and individual computing devices, including user support, troubleshooting, repair, optimization of computing power;

- Organization of uninterrupted functioning of computing devices and networks, including ensuring operability necessary devices uninterruptible power supply, air conditioning, energy supply, backup data storage, quick recovery;

- Integration of corporate information systems with external cloud services, computer systems with IP telephony systems, physical security systems;

- Ensuring reliable, stable and safe functioning of application software systems;

- Setting up, testing, administering and maintaining the operation of various organizational equipment within effective systems remote control;

- Introduction of new information technologies, new hardware solutions, new IT services and new methods of managing the hardware of information systems of modern enterprises;

- Optimization of technical and economic indicators of computer complexes, systems and networks;

- Project management for optimization of computer networks and systems, implementation of new information and telecommunication technologies;

- Coordination of team activities system administrators, network and technical support engineers.

Profile disciplines:

- Network technologies and system administration;

- Data storage systems and networks;

- System and application software;

- Computing systems, networks and telecommunications;

- Data protection;

- Networks and communications;

- Diagnostics and reliability of automated systems.

Graduates are in demand in almost any organization and any enterprise. Large corporations, banks, insurance companies, government agencies, and municipal authorities have especially high demand for graduates. Intensive professional development awaits graduates in information and telecommunications companies, small innovative enterprises in the IT field, and system integrator companies.

Graduates occupy positions of network administrators, engineers and heads of IT departments, engineers technical support, network and telecommunications equipment engineers, information security specialists, IT consultants. Graduates can build their own business and develop as an IT entrepreneur.

A set of technical and software, intended for information services for people and technical objects, is called a general term data processing system. Another umbrella term is Information system.

If the information system is used to manage technical systems, it is often called information management system. These are the most common names for systems of this purpose.

VM is one of the classes of information systems. In addition to the VM class, these include VC, VS and networks. Let us consider the main distinguishing features of these classes of information systems.

The VM is designed to solve a wide range of problems by users working in various subject areas (solving mathematical problems, word processing, accounting, games, etc.). The main block of the VM, which converts information and controls the computing process based on the program, is the processor. (The word "processor" is derived from the word "process") The processor initiates and manages the process of program execution.

Computing complex– these are several VMs (or computing systems) informationally interconnected (usually via a serial channel). Moreover, each VM independently manages its own computational processes, and intensive ones (in comparison with the information interaction of processors in multiprocessor systems). VC is especially widely used in information management systems. Control objects in technical systems often have a significant extent in space and contain big number units, technological installations, etc. As tools and technologies develop computer networks information and management systems use modern telecommunications, and the information and management system is implemented in the form of a local computer network, not VK.

Computer system call an information system configured to solve problems in a specific area of application, i.e. it has hardware and software specialization to improve performance and reduce cost. Often, a computer contains several processors, between which intensive information exchange occurs during operation, and which have a unified control of computing processes. Such systems are called multiprocessor. Another common type of aircraft is microprocessor systems. They are built using either a microprocessor (MP), a microcontroller, or a specialized digital signal processor. Typically, such systems are specialized for tasks local control and control of technological equipment in technical and household systems. The corresponding aircraft are often called built-in aircraft.

A distinctive feature of networks as a class of information systems is the developed functions of information interaction.

The means of transmitting and processing information in the network are focused on the collective use of network-wide resources - hardware, information and software. Subscriber system is a set of VMs, software, peripheral equipment, and means of communication with a telecommunication subsystem (communication subnetwork). Communication subsystem– a set of physical information transmission media, hardware and software that ensure information interaction between subscriber systems.

As a physical medium for transmitting information, they use twisted pair, cable, optical fiber, electromagnetic waves.

Information systems equipment, including computing and telecommunications devices, is called hardware(hardware).

Order 343 mail. Order by Russian post. Consequences of failure to appear in court when summoned

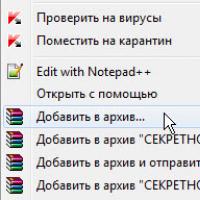

Order 343 mail. Order by Russian post. Consequences of failure to appear in court when summoned How to put a password on a folder on a Windows computer without and with programs

How to put a password on a folder on a Windows computer without and with programs Pluton – Free Bootstrap HTML5 One Page Template

Pluton – Free Bootstrap HTML5 One Page Template History of ZX Spectrum: Myths and reality New Spectrum

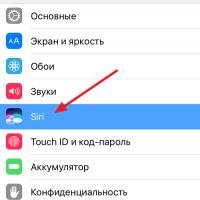

History of ZX Spectrum: Myths and reality New Spectrum Voice assistant Siri from Apple Siri functions on iPhone 6s

Voice assistant Siri from Apple Siri functions on iPhone 6s How to roll back to a previous version of iOS?

How to roll back to a previous version of iOS? Unlock iPad in four days

Unlock iPad in four days